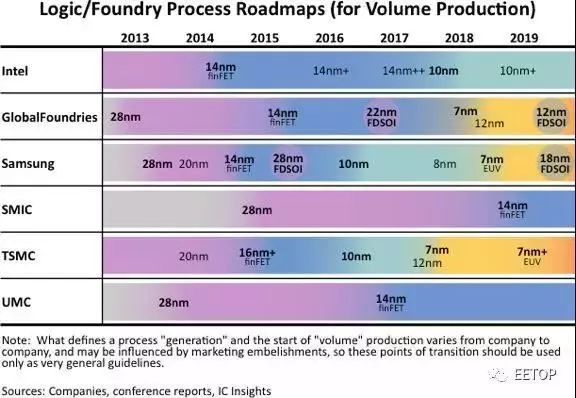

集成电路产业的发展取决于 IC 制造商是否有能力继续为消费者提供更多的性能和功能。随着主流 CMOS 工艺在理论、实践和经济方面的限制,降低集成电路的成本 (按功能或按性能) 比以往任何时候都更加关键和具有挑战性。IC Insights 2019 年版的 McClean 报告显示,企业提供的面向逻辑的流程技术比以往任何时候都更加多样化。图 1 列出了公司目前使用的几种领先的高级逻辑技术。主要节点之间的每个过程生成的衍生版本巳成为常规事件。

以下是主要晶圆厂的最新工艺进展:

英特尔

其在 2018 年末发布的第九代处理器代号为“Coffee Lake-S”,有时也被称为“Coffee Lake Refresh.”。英特尔表示,这些处理器是新一代产品,但它们似乎更像是对第 8 代产品的增强。细节尚不清楚,但这些处理器似乎是在 14nm++ 工艺的增强版上制造的,或者可以认为是 14nm++ 工艺。

英特尔将于 2019 年推动 10nm 工艺的大规模生产,首批使用这个工艺的产品将是 2018 年 12 月推出的“Sunny Cove”系列处理器。从目前看来,Sunny Cove 架构基本上取代了应该是原本计划在 2019 年推出的 10 纳米 Cannon Lake 架构。预计到 2020 年,10nm + 衍生工艺将进入批量生产阶段。

台积电

台积电的 10nm finFET 工艺于 2016 年底投入批量生产,短短两年间,他们巳经从 10 纳米迅速发展至 7 纳米。在台积电看来,7nm 产品将成为继 28nm 和 16nm 之后的又一个长寿命节点。

先进工艺方面,台积电 5 纳米工艺正在开发中,预计将于 2019 年上半年进入风险试产阶段,并于 2020 年进入量产。该工艺将使用 EUV,但它不会是台积电利用 EUV 技术的第一个工艺。根据台积电规划,他们将在 7nm 技术的改进版本 N7 + 工艺的关键层(四层)上使用 EUV 光刻机。但 N5 工艺将厂泛使用 EUV(最多 14 层)。N7 + 计划于 2019 年第二季度开始批量生产。

三星

在 2018 年初,三星宣布开始批量生产名为 0LPP(low power plus)的第二代

10nm 工艺。在 2018 年晚些时候,三星推出了名为 10LPU(low power ultimate) 的第三代 10nm 工艺,从另一个角度实现性能提升。与台积电不同的是,三星在10nm 工艺上使用三重图案光刻技术,且三星认为其 10 纳米工艺系列(包括 8 纳米衍生产品)的生命周期将会很长。

三星的 7nm 技术于 2018 年 10 月投入风险试产。与台积电不一样,三星不再提供采用浸没式光刻技术的 7nm 工艺,而是决定直接上马 EUV 的。据了解,三星该将 EUV 用于 7nm 的 8-10 层。

格芯

格芯公司将其 22nm FD-SOI 工艺视为其主要市场,并与其 14nm finFET 技术相辅相成。按照他们的说法,22FDX 平台的性能与 finFET 非常接近,但制造成本与 28nm 技术相同。

2018 年 8 月,GlobalFoundries 宣布将停止 7nm 开发。按照他们的说法,做出这个决定一方面是因为先进技术节点的生产成本大福增加,另一方面是大少的代工客户计划使用下一代工艺,因此他们对其战略进行了重大转变。公司也调整了其研发工作,以进一步增强其 14nm 和 12nm finFET 工艺及其完全耗尽的 SOI 技术的竞争力。

SMIC

前中芯国际第一代 FinFET 14nm 工艺巳经进入客户验证阶段,产品可靠度与良率进一步提升,同时 12nm 工艺开发也取得突破。根据媒体报道,中芯国际 14nm 工艺将在今年上半年投入大规模量产,良品率巳高达 95%。

五十年来,集成电路技术的生产力和性能有了惊人的提高。虽然这个行业巳经克服了摆在它面前的许多障碍,但这些障碍似乎越来越大。尽管如此,集成电路设计人员和制造商正在开发的解决方案似乎更具革命性,而非渐进性,以增加芯片的功能。